# 9. Programmable Machines

6.004x Computation Structures Part 2 – Computer Architecture

Copyright © 2015 MIT EECS

L09: Programmable Machines, Slide #1

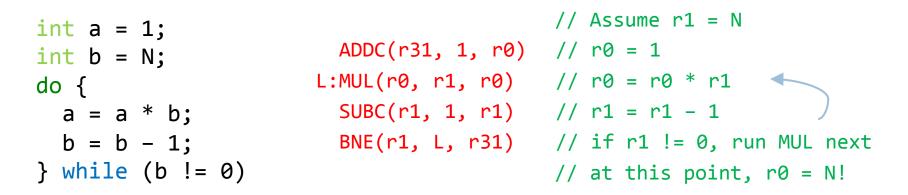

# Example: Factorial

factorial(N) = N! = N\*(N-1)\*...\*1

```

C:

int a = 1;

int b = N;

do {

a = a * b;

b = b - 1;

} while (b != 0)

initially: a = 1, b = 5

after iter 1: a = 5, b = 4

after iter 2: a = 20, b = 3

after iter 3: a = 60, b = 2

after iter 4: a = 120, b = 1

after iter 5: a = 120, b = 0

Done!

```

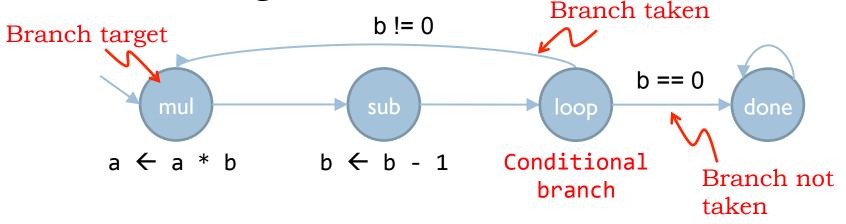

# Example: Factorial factorial(N) = N! = N\*(N-1)\*...\*1

**C**: int a = 1;int b = N;do { a = a \* b; b = b - 1;} while (b != 0) start:  $a \leftarrow 1$ ,  $b \leftarrow 5$ loop:  $a \leftarrow 5, b \leftarrow 4$ loop:  $a \leftarrow 20, b \leftarrow 3$ loop:  $a \leftarrow 60, b \leftarrow 2$ loop:  $a \leftarrow 120, b \leftarrow 1$ loop:  $a \leftarrow 120, b \leftarrow 0$ done:

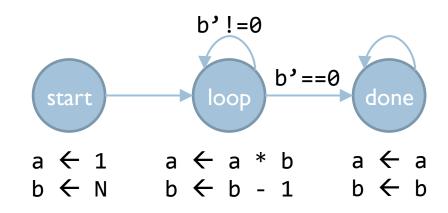

**High-level FSM:**

- Helpful to translate into hardware

- D-registers (a, b)

- 2-bits of state (start, loop, done)

- Boolean transitions (b'==0, b'!=0)

- Register assignments in states (e.g., a ← a \* b)

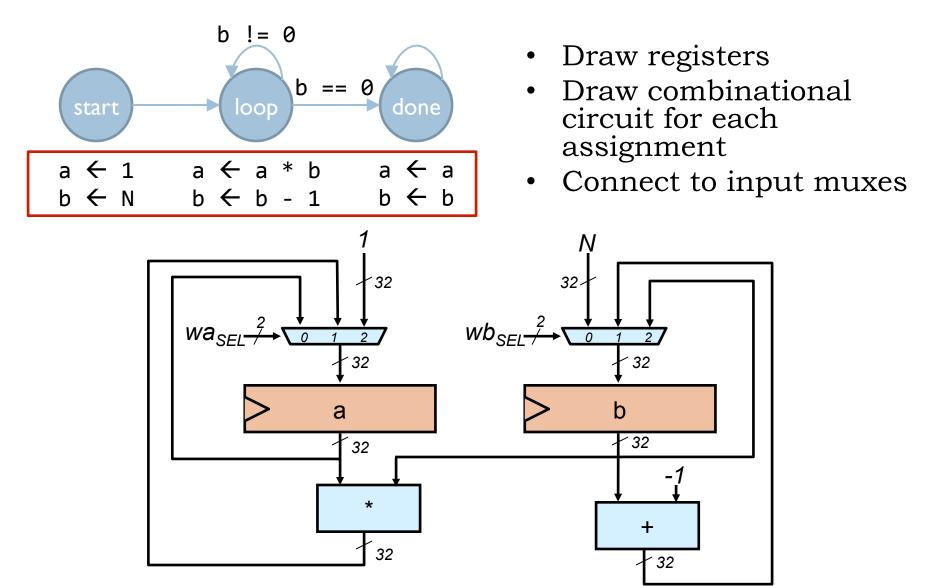

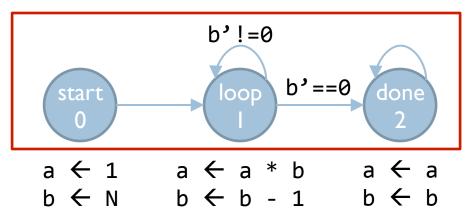

# **Datapath for Factorial**

# **Control FSM for Factorial**

- Draw combinational logic for transition conditions

- Implement control FSM:

- States: High-level FSM states

- Inputs: Transition logic outputs

- Outputs: Mux select signals

$$\rightarrow wa_{SEL}(2 \text{ bits})$$

$$\rightarrow wb_{SEL}(2 \text{ bits})$$

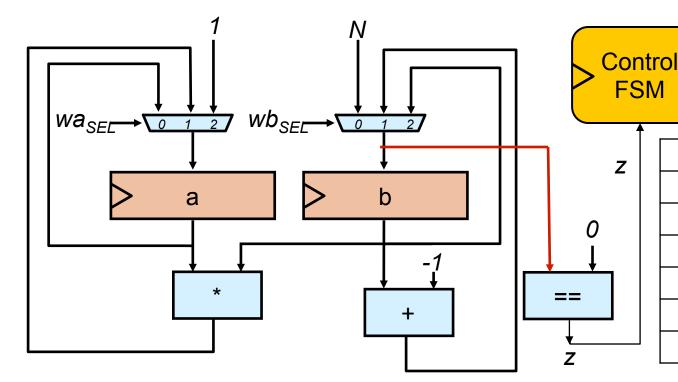

| S  | Ζ | wa <sub>sel</sub> | wb <sub>sel</sub> | S' |

|----|---|-------------------|-------------------|----|

| 00 | 0 | 10                | 00                | 01 |

| 00 | Ι | 10                | 00                | 01 |

| 01 | 0 | 01                | 01                | 01 |

| 01 | Ι | 01                | 01                | 10 |

| 10 | 0 | 00                | 10                | 10 |

| 10 | I | 00                | 10                | 10 |

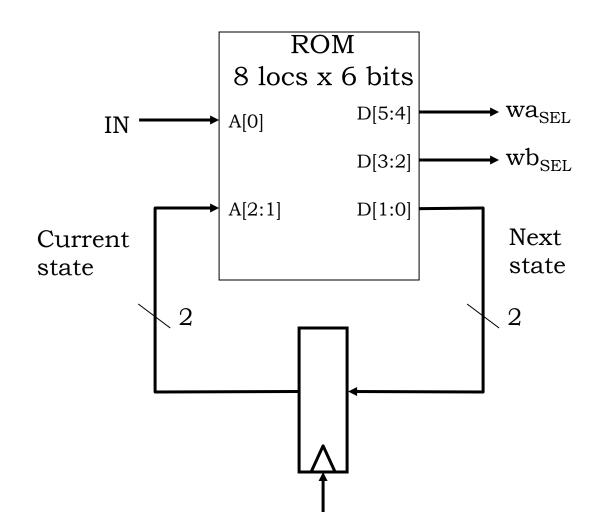

### **Control FSM Hardware**

#### ROM contents

| A[2:0] | D[5:0]   |  |

|--------|----------|--|

| 000    | 10 00 01 |  |

| 001    | 10 00 01 |  |

| 010    | 01 01 01 |  |

| 011    | 01 01 10 |  |

| 100    | 00 10 10 |  |

| 101    | 00 10 10 |  |

# So Far: Single-Purpose Hardware

- Problem→ Procedure (High-level FSM)→ Implementation

- Systematic way to implement high-level FSM as a datapath + control FSM

- Is this implementation an FSM itself?

- If so, can you draw the truth table?

- How should we generalize our approach so we can solve many problems with one set of hardware?

- More storage for operands and results

- A larger repertoire of operations

- General-purpose datapath

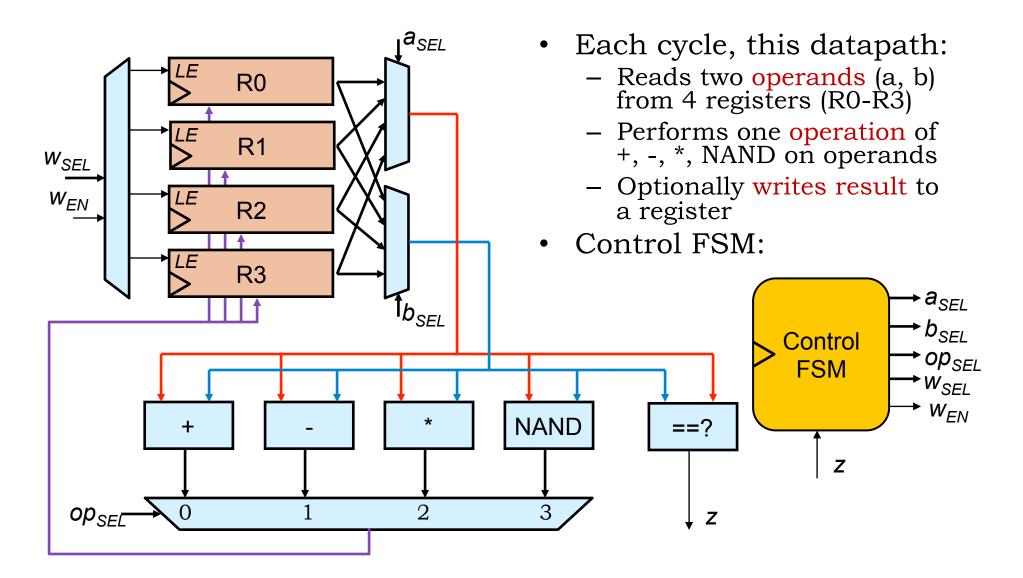

### A Simple Programmable Datapath

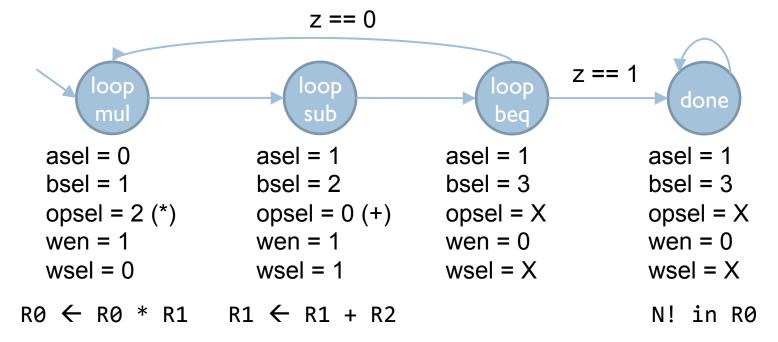

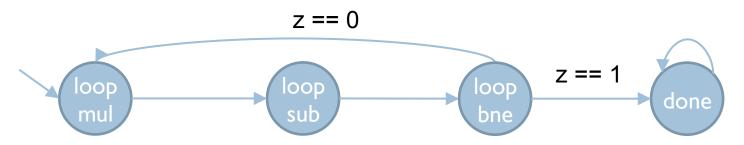

# **A Control FSM for Factorial**

• Assume initial register contents:

R0 value = 1 R1 value = N R2 value = -1 R3 value = 0

• Control FSM:

# New Problem $\rightarrow$ New Control FSM

- You can solve many more problems with this datapath!

- Exponentiation, division, square root, ...

- But nothing that requires more than four registers

- By designing a control FSM, we are programming the datapath

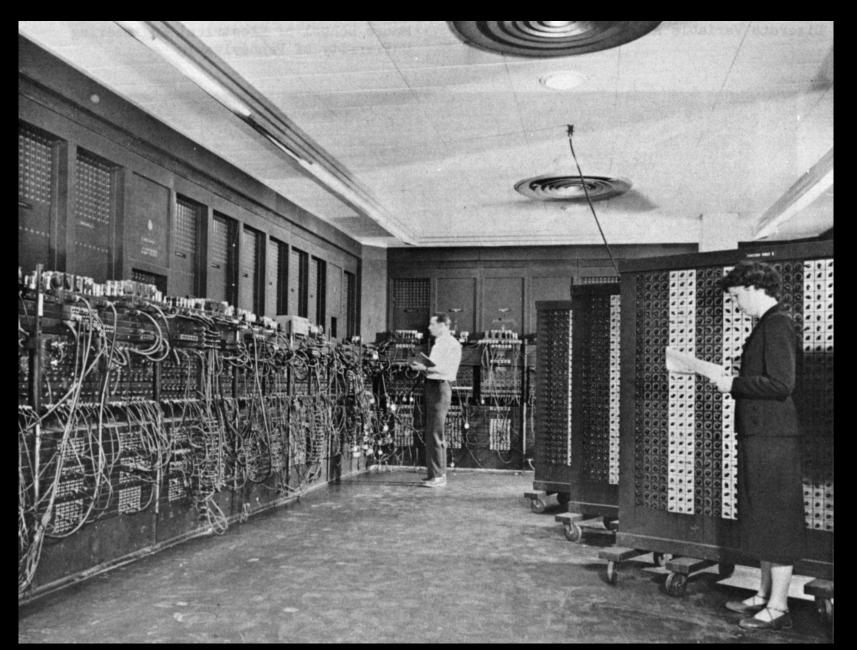

- Early digital computers were programmed this way!

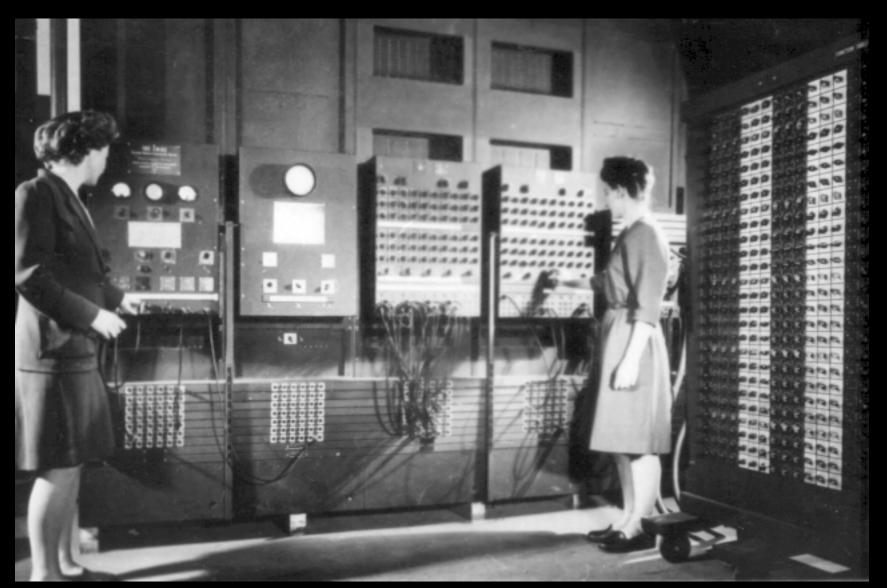

- ENIAC (1943):

- First general-purpose digital computer

- Programmed by setting huge array of dials and switches

- Reprogramming it took about 3 weeks

"Eniac" by Unknown - U.S. Army Photo.

6.004 Computation Structures

L09: Programmable Machines, Slide #11

U.S. Army Photo.

6.004 Computation Structures

L09: Programmable Machines, Slide #12

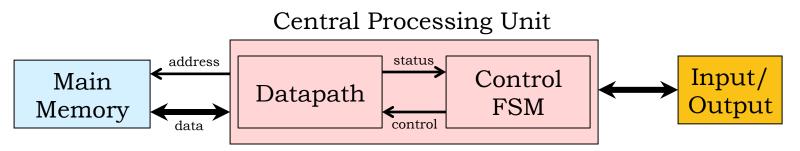

# The von Neumann Model

- Many approaches to build a general-purpose computer. Almost all modern computers are based on the von Neumann model (John von Neumann, 1945)

- Components:

• Central processing unit:

Performs operations on values in registers & memory

• Main memory:

Array of W words of N bits each

• Input/output devices to communicate with the outside world

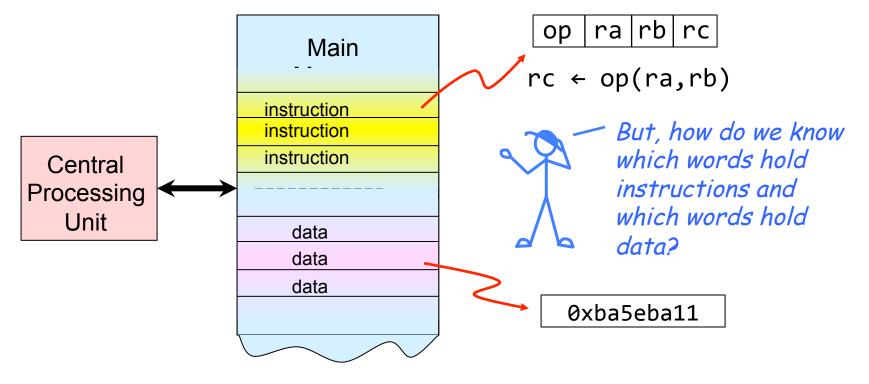

# Key Idea: Stored-Program Computer

- Express program as a sequence of coded instructions

- Memory holds both data and instructions

- CPU fetches, interprets, and executes successive instructions of the program

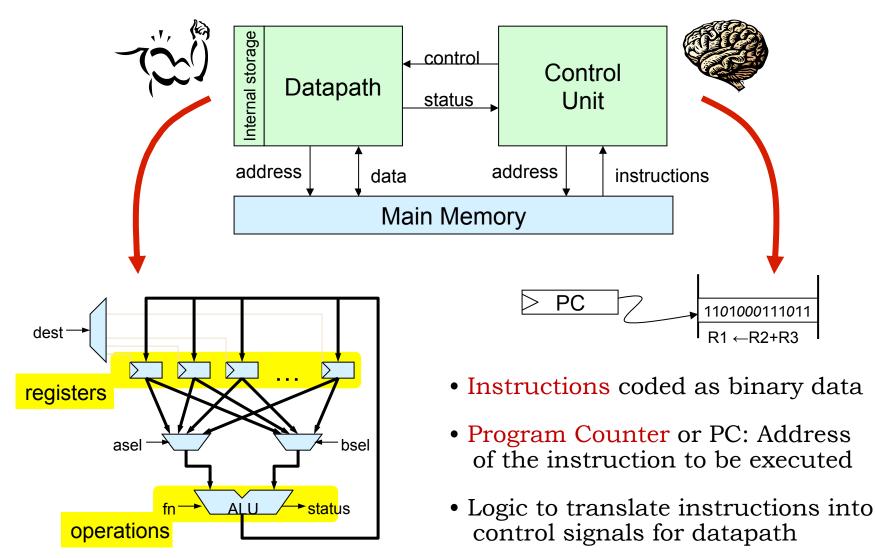

# Anatomy of a von Neumann Computer

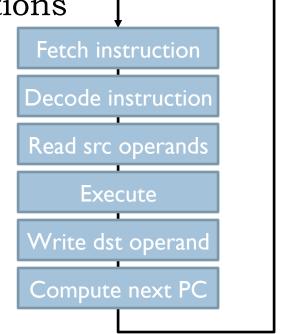

# Instructions

- Instructions are the fundamental unit of work

- Each instruction specifies:

- An operation or opcode to be performed

- Source operands and destination for the result

- In a von Neumann machine, instructions are executed sequentially

Fetc

- CPU logically implements this loop:

- By default, the next PC is current

PC + size of current instruction

unless the instruction says otherwise

# Instruction Set Architecture (ISA)

- ISA: The contract between software and hardware

- Functional definition of operations and storage locations

- Precise description of how software can invoke and access them

- The ISA is a new layer of abstraction:

- ISA specifies what the hardware provides, not how it's implemented

- Hides the complexity of CPU implementation

- Enables fast innovation in hardware (no need to change software!)

- 8086 (1978): 29 thousand transistors, 5 MHz, 0.33 MIPS

- Pentium 4 (2003): 44 million transistors, 4 GHz, ~5000 MIPS

- Both implement x86 ISA

- Dark side: Commercially successful ISAs last for decades

- Today's x86 CPUs carry baggage of design decisions from the 70's

# Instruction Set Architecture Design

- Designing an ISA is hard:

- How many operations?

- What types of storage, how much?

- How to encode instructions?

- How to future-proof?

- How to decide? Take a quantitative approach

- Take a set of representative benchmark programs

- Evaluate versions of your ISA and implementation with and without feature

- Pick what works best overall (performance, energy, area...)

- Corollary: Optimize the common case

Let's design our own instruction set: the Beta!

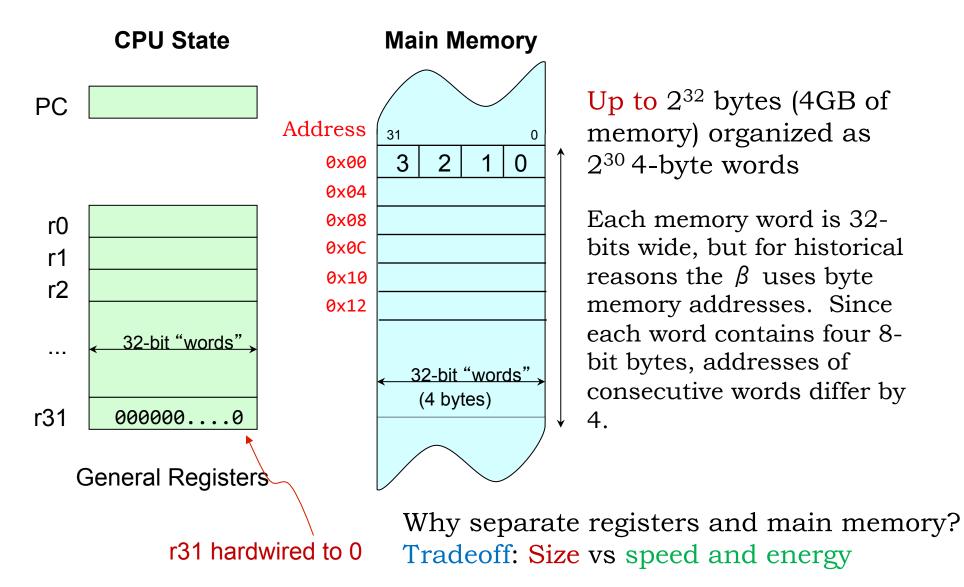

# **Beta ISA: Storage**

# Storage Conventions

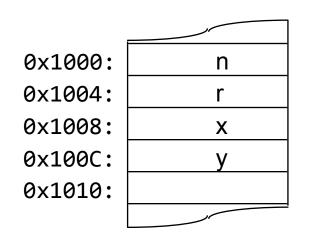

- Variables live in memory

- Registers hold temporary values

- To operate with memory variables

- Load them

- Compute on them

- Store the results

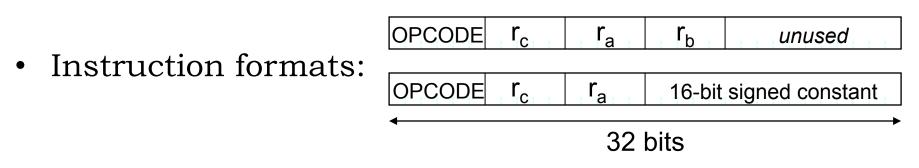

# **Beta ISA: Instructions**

- Three types of instructions:

- Arithmetic and logical: Perform operations on general registers

- Loads and stores: Move data between general registers and main memory

- Branches: Conditionally change the program counter

- All instructions have a fixed length: 32 bits (4 bytes)

- Tradeoff (vs variable-length instructions):

- Simpler decoding logic, next PC is easy to compute

- Larger code size

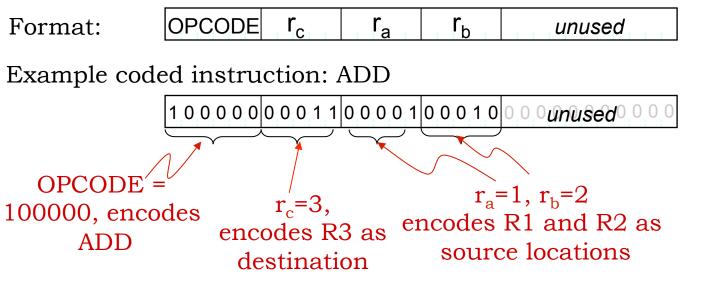

# **Beta ALU Instructions**

32-bit hex: 0x80611000 We prefer to write a symbolic representation: ADD(r1,r2,r3)

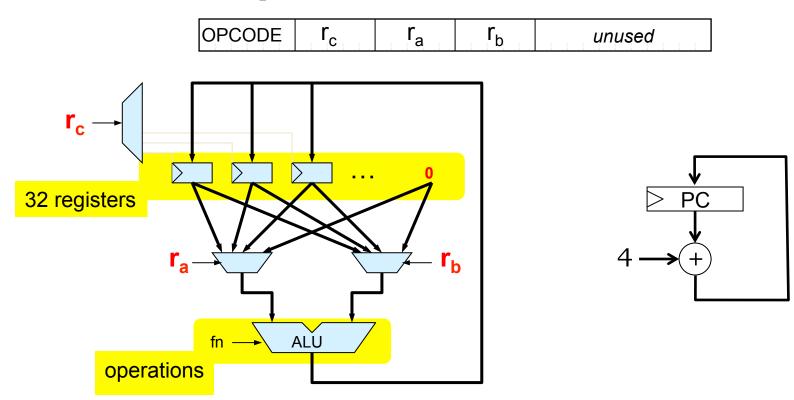

# Implementation Sketch #1

Now that we have our first set of instructions, we can create a more concrete implementation sketch:

# Should We Support Constant Operands?

Many programs use small constants frequently e.g., our factorial example: 0, 1, -1 Tradeoff:

> When used, they save registers and instructions More opcodes → more complex control logic and datapath

Analyzing operands when running SPEC CPU benchmarks, we find that constant operands appear in

- >50% of executed arithmetic instructions

*Loop increments, scaling indicies*

- >80% of executed compare instructions

*Loop termination condition*

- >25% of executed load instructions

Offsets into data structures

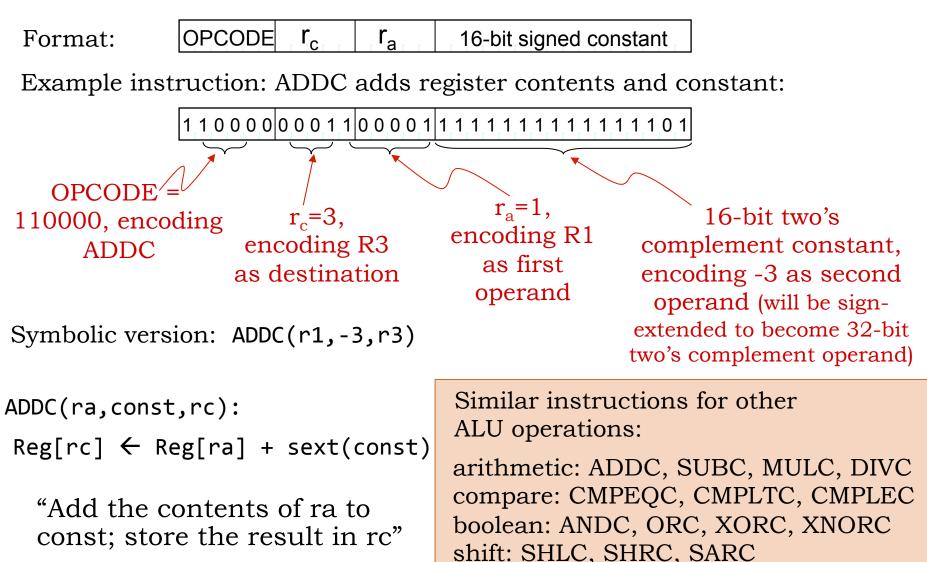

# **Beta ALU Instructions with Constant**

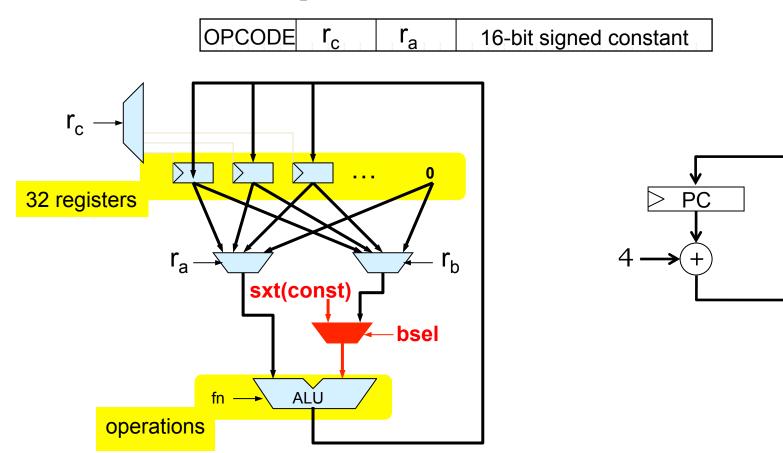

# Implementation Sketch #2

Next we add the datapath hardware to support small constants as the second ALU operand:

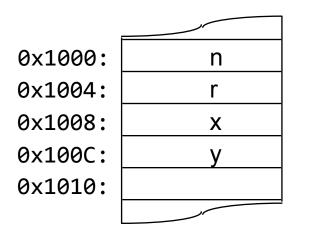

# **Beta Load and Store Instructions**

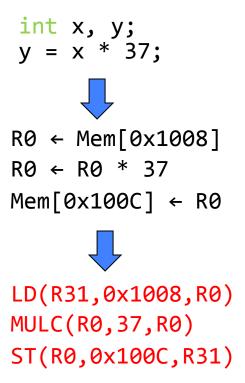

Loads and stores move data between the internal registers and main memory Address calculation

LD(ra,const,rc) Reg[rc] ← Mem[Reg[ra] + sext(const)]

Load rc with the contents of the memory location

```

ST(rc,const,ra) Mem[Reg[ra] + sext(const)] ← Reg[rc]

```

Store the contents of rc into the memory location

To access memory the CPU has to generate an address. LD and ST compute the address by adding the sign-extended constant to the contents of register ra.

- To access a constant address, specify R31 as ra.

- To use only a register value as the address, specify a constant of 0.

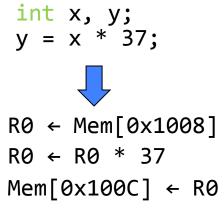

# Using LD and ST

- Variables live in memory

- Registers hold temporary values

- To operate with memory variables

- Load them

- Compute on them

- Store the results

#### Can We Solve Factorial With ALU Instructions?

• No! Recall high-level FSM:

- Factorial needs to loop

- So far we can only encode sequences of operations on registers

- Need a way to change the PC based on data values!

- Called "branching". If the branch is taken, the PC is changed. If the branch is not taken, keep executing sequentially.

# **Beta Branch Instructions**

The Beta's *branch instructions* provide a way to conditionally change the PC to point to a nearby location...

... and, optionally, remembering (in Rc) where we came from (useful for procedure calls).

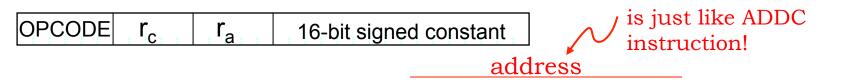

BEQ or BNE **r**<sub>c</sub> **r**<sub>a</sub> 16-bit signed constant

"offset" is a SIGNED CONSTANT encoded as part of the instruction!

offset = distance in words to branch target, counting from the instruction following the BEQ/BNE. Range: -32768 to +32767.

#### **Can We Solve Factorial Now?**

• Remember control FSM for our simple programmable datapath?

- Control FSM states  $\rightarrow$  instructions!

- Not the case in general

- Happens here because datapath is similar to basic von Neumann datapath

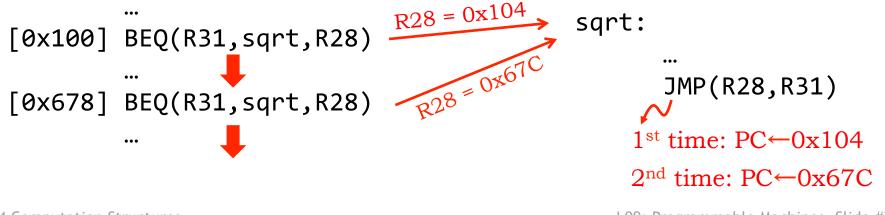

### **Beta JMP Instruction**

Branches transfer control to some predetermined destination specified by a constant in the instruction. It will be useful to be able to transfer control to a computed address.

> 011011  $r_c$   $r_a$  unused JMP(Ra,Rc): Reg[Rc]  $\leftarrow$  PC + 4

PC ← Reg[Ra]

Useful for procedure call return...

6.004 Computation Structures

L09: Programmable Machines, Slide #32

# **Beta ISA Summary**

- Storage:

- Processor: 32 registers (r31 hardwired to 0) and PC

- Main memory: 32-bit byte addresses; each memory access involves a 32-bit word. Since there are 4 bytes/word, all addresses will be a multiple of 4.

- Instruction types:

- ALU: Two input registers, or register and constant

- Loads and stores

- Branches, Jumps